안녕하세요. 옆집 컴공생입니다. 오늘은 I/O module(입출력모듈)에 대해서 살펴보겠습니다.

아래 포스팅은 저번 시간에 배웠던 External Memory 입니다.

https://com24everyday.tistory.com/148?category=1125097

컴퓨터구조6 External Memory

안녕하세요. 옆집 컴공생입니다. 오늘은 챕터6 'External Memory' , 외장메모리 특히 하드디스크에 대해 배워보겠습니다. 저번 포스팅에서는 'Internal Memory' 에 대해 알아보았었습니다. https://com24everyday

com24everyday.tistory.com

입출력 모듈는 왜 필요할까요?

다양한 장치가 존재하는데 각자의 속도는 다 다릅니다. 출력 데이터 포맷도 다 다르고 그래서 일반화 할 수 는 없을까 해서 만들어진 것이 'I/O module' 입니다. (CPU와 RAM보다 속도도 느리기 때문에 버퍼링 할 수 있는 게 필요 했습니다.)

I/O module의 역할

-CPU 와 Memory 의 인터페이스

- 주변 장치간의 인터페이스

시스템 버스에는 CPU 와 Memory 가 붙습니다. 그리고 아래 쪽에 실제 디바이스가 위치하겠죠.

포맷을 해주고 속도를 조절해주고 동기화 시켜주는게 I/O Module 의 역할입니다.

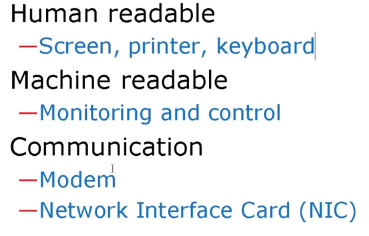

External Devices

다음과 같이 다양한 장치들이 있습니다.

이런 다양한 장치들을 I/O module가 추상화해줍니다.

External Device Block Diagram

여기에서 I/O module 은 어디에 있을까요?

이건가요? 아닙니다. 이건 실제 external device 쪽에 interface를 의미합니다.

I/O module 로 부터 Control signal이 옵니다. 실제 디바이스에게 이 신호가 가는데 이에 대한 상태를 다시 I/O module로 전달하기도 합니다.

데이터 같은 경우는 Buffer를 통해서 데이터를 동작할 수 있는 에너지 형태로 바꾸는 역할을 합니다.

Transducer 을 이해할 필요가 있습니다.

I/O module 에선 Buffer 로 신호가 오는 건 결국 디지털화된 전기 시그널 입니다. 이걸 쓸 수 있도로 바꾸는게 트랜스듀서입니다. 이는 변환기라고 합니다.

다음과 같이 에너지를 변환해주는 겁니다.

I/O Module 의 기능

-Control and timing : 내부 리소스와 외부장치 트래픽 조절

-Processor communication

-Device communication

-Data buffering : 빠른 내부 장치, 느린 외부 장치 조절

-Error detection

I/O Steps

1. CPU 가 I/O module 장치 상태 체크

2. I/O module 상태 반환

3. 준비 돼 있으면 데이터 전송 요규

4. I/O module 이 장치로 부터 데이터 가져옴

5. I/O module이 데이터를 CPU 에게 전달

다음은 I/O module의 다이어그램입니다.

보면 외부장치인터페이스 로직이 여러개입니다. 시스템버스 인터페이스도 있다면 왼쪽에 CPU 와 Memory 가 있겠죠. 왼쪽 Lines 들은 다 인터페이스인 겁니다.

데이터가 적절히 I/O logic에서 변환되어 외부 장치로 가는 겁니다.

"즉 I/O module 은 타이밍 이나 포맷과 같은 복잡한 사항을 도맡아 해줍니다. CPU는 오직 I/O module 하고만 통신을 합니다. "

Input Output Techniques

1. Programmed I/O : CPU must wait

2. Interrupted-driven I/O

3. Direct memory acess(DMA) : CPU 에 개입 없이 다른 게 직접 수행

모든 게 프로그램에 의해서, 즉 CPU가 전체적인 동작을 합니다.

여기서는 CPU 가 요청을 하고 Do something else 하는 것을 볼 수 있죠. Programmed I/O 에서는 계속적인 CPU 의 개입이 있었으나 CPU 는 기다리고 있었습니다. 하지만 여기선 인터럽트를 받아서 CPU 가 다른 일을 하게 됩니다.

위 기술들은 CPU가 데이터를 읽고 쓰고 다 했습니다. 하지만 여기서는 CPU 가 Read block command 를 보내면 DMA 라는 게 다 처리를 하게 됩니다.

I/O Device 는 식별하기 위한 address가 있습니다. Memory를 바라보는 것과 동일하게 I/O Devices를 바라봅니다.

I/O Mapping

-Memory mapped I/O : 메모리가 CPU가 관리하는 공간에 하나의 주소로 맵핑되어 있습니다. 특정 메모리 주소는 특정 장치를 가리킵니다. 아래 그림을 통해 메모리와 device를 동일한 레벨로 대한다는 걸 알 수 있습니다.

-Isolated I/O : address 공간이 분리가 되어있고 특별한 I/O command 가 있습니다.

다음 그림은 둘의 차이를 보여줍니다.

Isolated I/O 와 Memory Mapping I/O

Isolated I/O은 프로그래머가 이해하기 쉬우나 메모리 공간이 입출력을 위해 사용됩니다. (메모리 낭비)

Interrupt Driven I/O

: 입출력을 위해 CPU 의 동작을 멈춥니다.

다음은 Interrupt 가 일어났을 때의 Processing 입니다.

사용자 프로그램 쪽 N 명령어에서 인터럽트가 일어났습니다.

여기서 인터럽트가 일어나면 Program Counter 와 General Registers 에서 Context Switching 이 일어나게 됩니다. (인터럽트 루틴을 실행시켜주기 위해서)

그래서 PC와 GR 은 Stack 에 저장이 됩니다. (T주소)

PC 는 새로운 Y 를 받아옵니다. (Interrupt Service Routine) Y + L 까지 실행이 됩니다.

T 에 저장했던 PC,GR 을 복구 시킵니다.

여러 Interrupt 가 발생이 했을 때 어떤 입출력 모듈에 의해서 발생했는지 알아보겠습니다.

Identifying Interrupting Module

- Different line for each module : 각각 하나씩 모듈이 다 있는건데 현실적으로 불가능

- Software poll : 소프트웨어적으로 CPU 가 하나씩 다 물어봄(느림)

- Daisy Chain or Hardware poll :

보면 하드웨어적으로 이렇게 쭉 연결이 되어 있는 겁니다.

시그널을 보내면 우선순위가 높은 거와 연결이 되어있으니 ' 너가 보냈니?' 라고 물어보고 맞을 때는 더이상 나아가지 않습니다. 아니라면 다음까지 나아가겠죠.

-Bus Master : 특별한 구조를 취해서 , master - slave 방식, PCI&SCSI

사례를 들어보겠습니다.

아주 예전에 사용하던 8259A Chip 이라는 Interrupt Controller 를 확인하겠습니다.

시그널을 받는데 여기서 8개의 디바이스 그리고 이 각각의 디바이스에 또 8개가 연결되어 있기 때문에 64개를 가지고 있습니다. 64개의 인터럽트를 처리할 수 있다는 겁니다. 윗쪽이 우선순위가 높습니다.

Direct Memory Access(직접 메모리 접근)

이제 굉장히 중요한 DMA 에 대해 배워보겠습니다. 원래 메모리 접근은 CPU 가 주관했습니다.

하지만 이게 아니라 I/O 가 직접 메모리에 쓰는 방식이 DMA 방식입니다.

이는 추가적으로 DMA module 이 필요합니다. (Controller도)

이 모듈은 CPU 의 권한을 위임 받아서 사용하게 되는데 CPU 가 메모리를 사용하지 않을 때 써야합니다.

(Cycle stealing, Block transfer, Interleaved DMA 방식이 있습니다. )

Cycle stealing : CPU 가 DMA 를 위한 별도의 프로토콜을 만든게 아니라 CPU의 사이클을 훔친겁니다.

이게 어떻게 되는 거냐면 word 단위로 DMA가 이루어집니다.(한 클럭동안 훔침)

원래 시스템 클럭과 ^INHIBIT AND 됩니다.

^INHIBIT 켜지면 System clock 이 안 움직이는 겁니다. (CPU 는 자기가 멈춰졌는지도 모릅니다.)

그럼 이런 ^INHIBIT은 누가 만들까요? DMA Controller 가 만듭니다.

다른 두가지 방식과 다르게 Cycle Stealing 은 CPU 가 인지를 하지 못하는 상황에서 발생합니다.

CPU 는 DMA controller 에게 다음과 같은 정보를 보냅니다.

-Read/Write

-Device address

-Starting address of memory block for data

-Amount of data to be transferred

CPU 의 역할을 DMA 가 하기 때문에 정보를 주는 겁니다.

이 때 CPU 는 다른 일을 하다가 DMA 의 인터럽트를 받습니다.

그럼 DMA 의 내부 구조에 대해 살펴보겠습니다.

Data Count : 얼마나 많은 데이터를 전송을 할 것이냐

Data register : 실제 전송되는 데이터 저장되는 장소

Address register : 메모리의 어떤 주소 영역인지

Control logic

DMA Configuration(DMA 의 구조)

이런 구조나

이런 구조 등이 있습니다.

DMA 동작 예시

1.입출력 장치인 Disk Cntroller 가 DMA 를 하고 싶다고 요청 (DREQ)를 보냅니다.

2.이때 chip이 데이터버스를 잡아도 되는지 즉 Hold 를 해도 되는지 요청을 보냅니다. (HRQ activate)

3.그럼 CPU 에서는 허락 신호를 보냅니다.

4.그리고 CPU 에게 승인 받았다는 사실을 DMA 가 입출력 장치에 알려줍니다. (DACK)

4-1.그럼 이제 데이터들이 DMA chip 에 셋팅이 될겁니다.

5. 그럼 입출력 장치가 그 데이터들을 Data bus를 통해 읽습니다.

6. 그리고 읽은 내용을 Main memory 에 씁니다.

7. 다 끝나고 나면 DMA 는 이제 다 썼다는 의미의 신호(HRQ deactivate)을 CPU 에게 보냅니다.

Fly-By : Device 에 DMA chip 가 내장이 되어있기 때문에 데이터가 DMA chip에 저장이 되지 않는 방식

'공부 > 컴퓨터 구조' 카테고리의 다른 글

| 컴퓨터구조10 Instruction Sets : Characteristics and Functions (0) | 2020.06.29 |

|---|---|

| 컴퓨터구조9 Computer Arithmetic (0) | 2020.06.23 |

| 컴퓨터구조6 External Memory (0) | 2020.06.13 |

| 컴퓨터구조5 Internal Memory (0) | 2020.06.12 |

| 컴퓨터구조4 Cache Memory (0) | 2020.06.05 |