안녕하세요. 옆집 컴공생입니다. 오늘 배운 논리회로설계 복습할건데... 교수님이 진도를 아주 엄청나게 시더라구요.(필기하면서 진땀 다 뺐습니다.) 복습하는데도 한참 걸릴거 같다는 느낌이 드네요. 오늘은 데이터패스 설계에 대해 자세히 배웠습니다. 아래 포스팅은 저번 시간 수업 내용입니다.

https://com24everyday.tistory.com/144

논리회로설계(레지스터 전송 수준에서의 논리설계방법)

안녕하세요. 옆집컴공생입니다. 저번 시간에는 레지스터 전송수준설계에 대해 배웠죠. 오늘은 이에 대해 더 배워보겠습니다! https://com24everyday.tistory.com/138 논리회로설계(레지스터전송수준설계)

com24everyday.tistory.com

그럼 복습하러 갑시다!

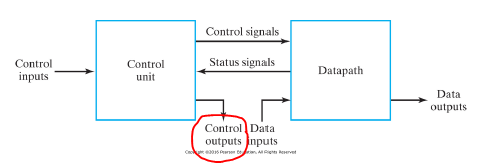

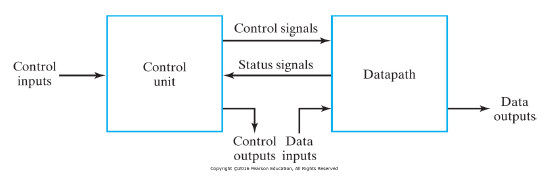

레지스터 전송 수준 설계에서 중요하게 생각해야하는 두가지가 뭘까요?

1. 전송 순서

2. 레지스터 전송 과정에서 필요한 가공

이 둘을 위해서 각각을 전담하는 전담블럭을 따로따로 만들게 됩니다.(똑똑한 사람들이 만들었습니다.)

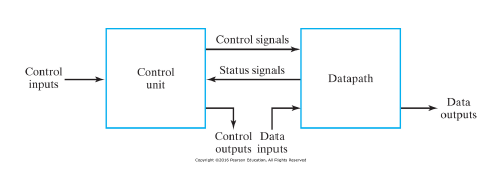

1. 올바른 전송 순서를 전담하는 블럭 Control Unit

2. 레지스터 전송 과정에서 필요한 가공을 전담하는 블럭 Datapath

즉 데이터패스에서 레지스터 전송들이 일어나면서 이 전송과정에서 가공도 함께 일어나야 됩니다.

그런데 이 전송 과정에서 중요한 순서들을 지켜야하는데 순서대로 일어나도록 Control Unit 에서 제어합니다.

위 그림의 Control signal 들은 제어부 입장에서는 출력이고 Datapath 입장에서는 입력입니다.

위 그림의 Status signal 은 데이터패스에서 일어나는 레지스터 전송과 가공 과정에서 일어나는 상황을 제어부에 알리는 역할입니다. 데이터패스 쪽에서 출력이고 제어부 입장에서는 입력입니다.

▶Control signals의 예

만일 데이터패스에서 A <- B+C 라는 트랜스퍼가 일어나야 한다면 이 트랜스퍼가 어느 클럭 사이클에서 일어나야 할지를 Control signals이 데이터패스에 알려줘야 합니다.

외부에서 레지스터 트랜스퍼의 순서를 변경하고자 하는 경우에는 Control inputs 입력으로 전달합니다.

이 제어부가 그렇게 수행하겠다고 외부에 응답하는 것은 Control outputs 출력을 통해 전달 합니다.

제어부, Control unit 에 레지스터가 있을 수 있을까요?

레지스터는 소프트웨어에 변수와 같다고 계속 언급이 되었습니다. 이와 같이 생각하면 제어부에 있을 필요가 없습니다.

왜냐하면 실제 데이터 가공은 데이터 패스에서 일어나고 제어부는 단지 순서를 결정하는 역할이기 때문에 레지스터가 없는겁니다. 그리고 제어부가 조합회로는 아니고 순차회로입니다.

순차회로인데 레지스터가 왜 없냐구요? 레지스터가 아니라 플립플롭만 존재하는 겁니다. 레지스터는 플립플롭으로 구성되지만 플립플롭은 레지스터가 아닙니다.

앞으로 하드웨어 설계할 때는 99% 의 확률로 레지스터 전송수준에서 설계가 됩니다. 항상 처음에는 아래와 같은 구조를 생각해야합니다.

제어부(Control unit)는 4장 설계법 따르면 됩니다. 제어부의 설계 순서는 다음과 같습니다.

상태천이표 또는 상태천이도를 만듦 -> 상태할당 -> 최적화된 부울식 -> 스키메틱 그림

여기에서 '상태천이표 또는 상태천이도를 만듦'는 부분은 Control Unit 에 대한 레지스터 수준 설계를 하는 겁니다.

나머지, 상태 할당하고, 최적화된 부울식 구하고 스키메틱 그리는게 Control Unit 에 대한 게이트 수준 설계 하는겁니다.

▶레지스터 전송 수준에서의 설계 : 상태천이표 또는 상태천이도 그리는 것

▶게이트 전송 수준에서의 설계 : 나머지

지금부터 배울 것은 데이터패스에 대한 레지스터 전송수준에서의 설계입니다.

Control Unit 에 대한 레지스터 전송수준에서의 설계와는 완전 다릅니다.

간단한 예로, 만일 데이터 패스에 'R2 <- R1' 같은 레지스터 전송이 필요하다면

데이터패스의 레지스터 전송수준설계는 다음과 같습니다.

왜 데이터패스의 레지스터 전송 수준 설계가 CU 와는 다르냐?

-> CU에 레지스터가 없기 때문

그럼 CU의 레지스터 전송 수준 설계는 왜 데이터패스와 다르냐?

-> 데이터패스에 대한 상태천이표, 천이도를 만들 수가 없기 때문( 상태 수가 너무 많기 때문에, 8비트 레지스터가 2개 있어도 2^16)

▶결과적으로 데이터패스에 존재하는 많은 수의 레지스터 그리고 레지스터의 비트 수로 인하여 데이터 패스에 대한 상태 천이표를 만드는 건 불가능합니다.

본격적으로 데이터패스의 설계 방법에 대해 배워보겠습니다.

데이터패스에 대한 설계의 출발점은 레지스터 전송표기법입니다.

그리고 레지스터 전송 과정에서는 단순 전송과 비단순전송로 2종류가 있습니다.

비단순 전송에서 가공이 일어나서 전송이 됩니다.

가공을 위해서는 조합 회로가 필요하죠.

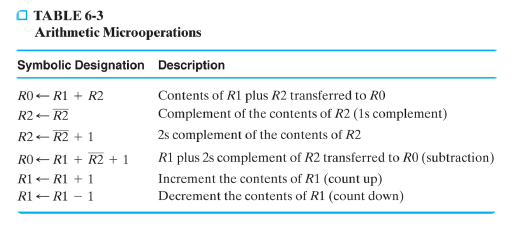

가공의 종류는 다음과 같습니다.

- 연산 관련 가공

- 논리 관련 가공

비단순 전송을 책에서는 microperation 이라고 합니다.

(가공예시)덧셈, 이진보수에 기반한 뺏셈, 1's 보수, +1, -1 관련된 레지스터 전송표기법 등의 가공등이 있습니다.

구체적인 예를 들어보겠습니다.

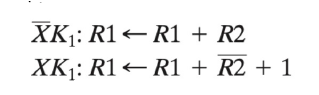

다음과 같은 2개의 레지스터 전송표기가 있습니다.

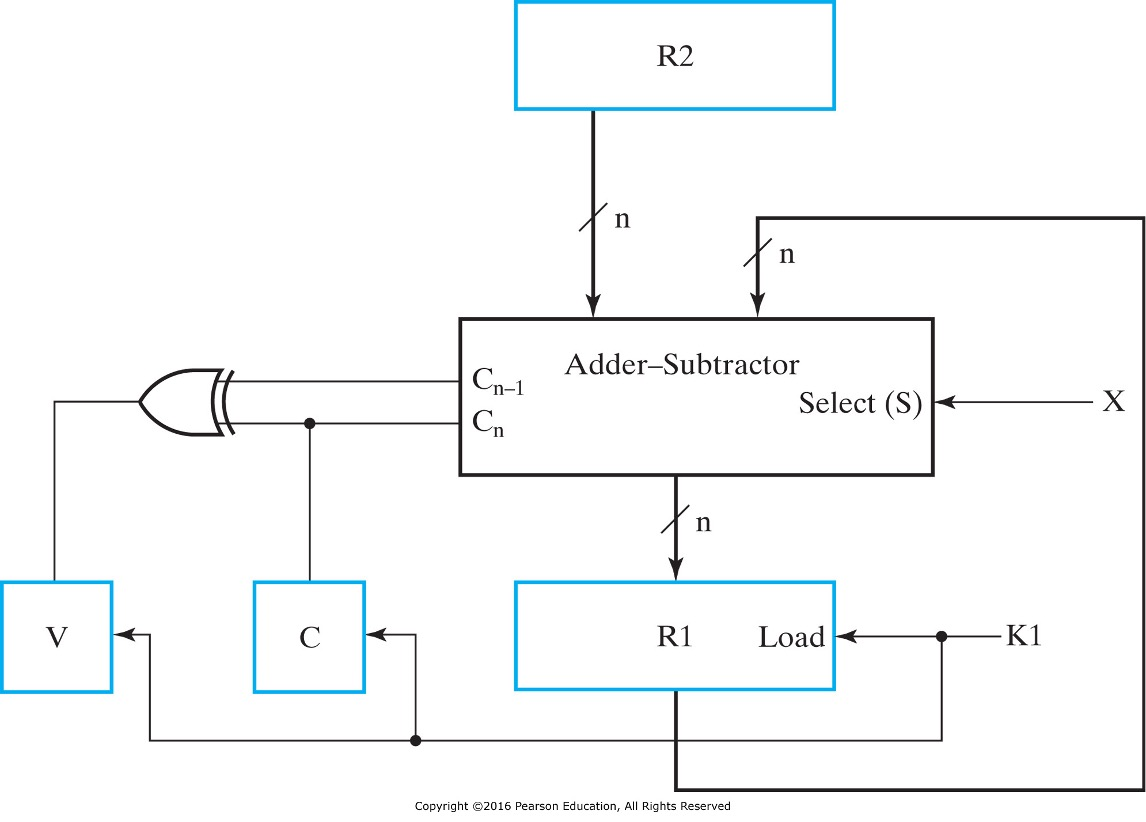

첫번째 줄은 X = 0일때 R1 와 R2를 더해서 R1으로 전송하고 시점은 K1 =1 일때,

두번째 줄은 X = 1일때 R2의 내용을 2의 보수해서 R1과 더해서 (즉 R1에서 R2 빼서) R1으로 전송하고 시점은 K1 =1 일때

레지스터 트랜스퍼가 일어나게 됩니다.

이 레지스터 전송 표기법 2개에서 데이터패스를 레지스터 전송 수준에서 설계를 해보겠습니다.

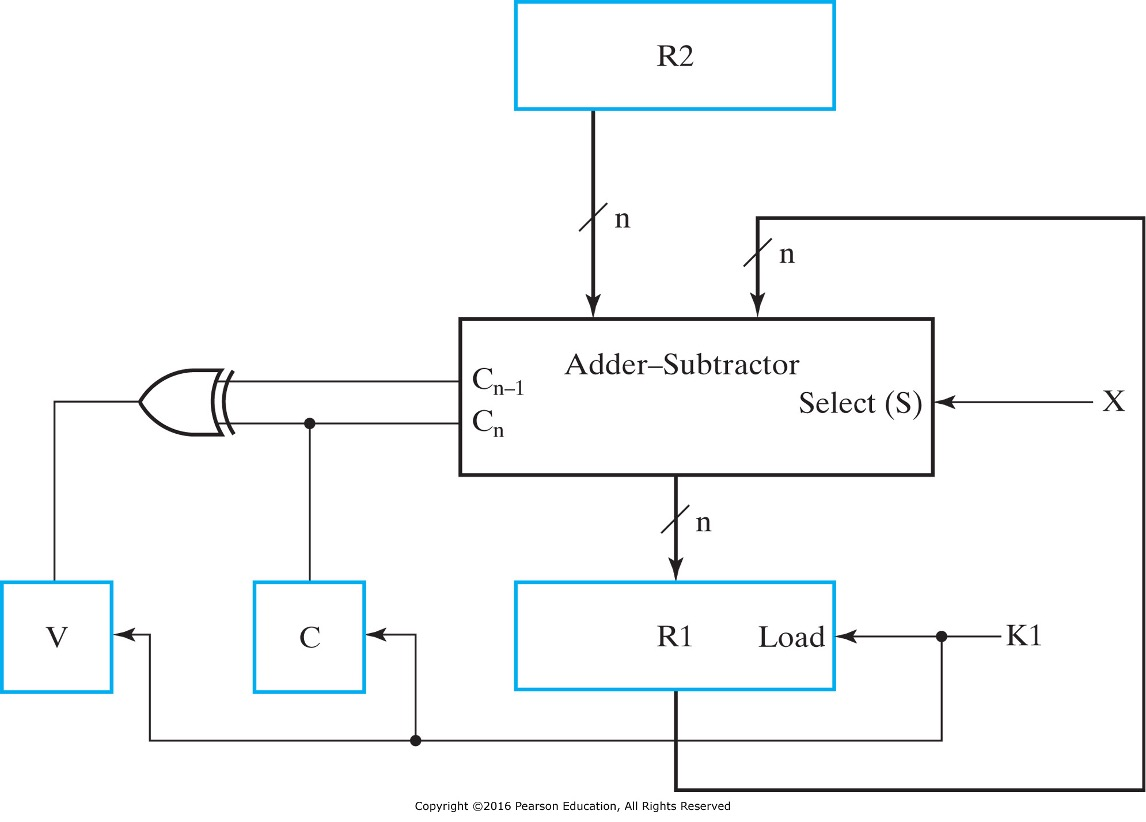

먼저 완성도 회로의 모습을 보여드리겠습니다.

우선, 두개의 레지스터 전송은 동시에 일어날 수 없습니다.

그래서 가공이 덧셈, 뺄셈을 해야하는데 동시에 일어날 수 없으므로 그냥 덧셈/ 뺄셈이 가능한 아래의 조합회로를 사용하자고 설계에서 결정을 내립니다.

▶그리고 레지스터는 2개 R1,R2 가 필요합니다.

▶그 다음에는 결과가 R1에 다시 저장이 되니깐 Carry Out 을 고려한 1-비트 플립플롭 C

▶그리고 연산 과정에서 오버플로우를 디텍드하기 위한 EXOR 게이트를 추가합니다.

▶이것의 출력은 V플립플롭의 D 입력으로 연결됩니다.

▶C 플립플롭의 D입력은 덧셈/뺄셈기의 Cn 연결 합니다.

그리고 덧셈/뺄셈기의 n비트 SUM 출력은 결과를 저장하는 R1의 입력으로 연결됩니다.

연산결과값은 K1 =1 일때 R1으로 로딩 되어야함을 레지스터 R1,C,V플롭의 LOAD 입력에 모두 K1 을 연결합니다.

마지막으로 X = 0 이면 덧셈, 1이면 뺄셈이기 때문에 Select 입력에 X를 연결합니다.

출력을 표시해주어도 되고 , clock 생략했습니다. 게이트 수준에서는 반드시 클럭을 그려야하짐나 레지스터 전송 수준에서는 생략이 가능합니다.

그럼 다음과 같은 회로가 만들어집니다.

아래 표는 논리 마이크로오페레이션의 예들을 보여주고 있습니다.

논리적 가공, NOT, AND, OR, EXOR 등등이 있습니다.

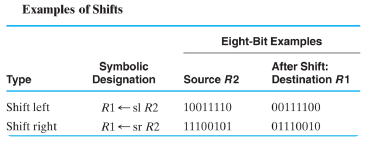

아래 표는 자릿수 이동인 쉬프트하는 걸 보여주고 있습니다.

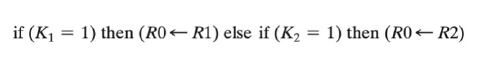

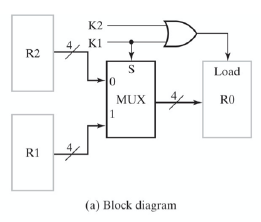

여기서 예로 사용된 레지스터 전송 표기법은 소프트웨어코드 스타일을 함께 사용해서 다음과 같은 식이 나옵니다.

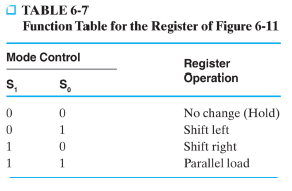

이것으로부터 레지스터 전송수준의 스키메틱은 다음과 같습니다.

여기서 MUX가 쓰인 이유는 무엇일까요?

이는 다음 시간에 알아보겠습니다!

수고하셨습니다.

'공부 > 논리회로설계' 카테고리의 다른 글

| 논리회로설계 (레지스터 수준 설계 과정) (2) | 2020.06.23 |

|---|---|

| 논리회로설계(레지스터 설계 예시, 비동기식 카운터 설계) (2) | 2020.06.22 |

| 논리회로설계(레지스터 전송 수준에서의 논리설계방법) (0) | 2020.06.12 |

| 논리회로설계(레지스터전송수준설계) (0) | 2020.06.10 |

| 논리회로설계(레지스터) (2) | 2020.06.04 |